ARM近日宣佈針對台積電28HPM(High Performance for Mobile, 移動高性能)製程技術,推出以ARMv8為架構的Cortex-A57與Cortex-A53處理器優化套件(POP) IP解決方案;POP IP產品現在可支援40奈米至28奈米的製程技術,此次同時發布針對台積電16奈米 FinFET製程技術的POP IP產品藍圖,可廣泛應用於各類Cortex-A系列處理器和Mali 繪圖處理器產品。

|

| ARM發布針對台積電16奈米 FinFET製程技術的POP IP產品藍圖 |

Cortex-A57與Cortex-A53處理器可獨立使用或互相搭配成big.LITTLE 處理器組合,以達到最佳的性能和功耗效率。多家率先獲得ARM授權採用28HPM製程Cortex-A57 POP IP的合作夥伴,已經開始進行設計實作。此外,針對16奈米FinFET製程技術的Cortex-A57與Cortex-A53 POP IP解決方案也將在2013年第四季度開放授權。

現有的28HPM解決方案產品組合,包括Cortex-A7、Cortex-A9、 Cortex-A15以及ARM Mali-T624 至Mali-T678 圖形處理器,將在全新的POP IP產品加入後而更臻完備。目前,ARM的合作夥伴已經將採用 POP IP技術的系統單晶片(SoC)出貨到市場上,這些系統單晶片正被應用於行動遊戲、數位電視、機上盒、行動運算和智慧手機等領域。

POP技術是ARM 全面實作策略中不可或缺的關鍵要素,能使ARM的合作夥伴得以突破功耗、性能與面積最佳化等限制,迅速地完成雙核與四核的實作。此外,這項技術還能協助以Cortex處理器為基礎的系統單晶片(SoC)進行實作最佳化、降低開發風險、並縮短產品上市的時程。

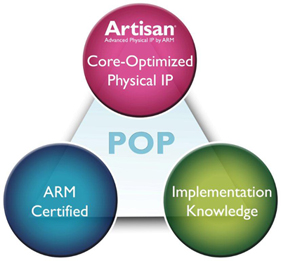

POP IP技術具備了實現ARM處理器實作最佳化的三大要件。首先,它包含了專門為ARM核心與製程技術調整過的Artisan實體IP邏輯庫和高速快取記憶體。這項實體IP的開發是透過ARM的實作經驗與處理器設計工程師緊密合作的結果。

第二部分是全面標竿測試報告,它記錄了ARM核心實作所需的確切條件和產生結果。最後一部分是詳細的實作說明,包括一份使用指南、晶片平面圖規劃、程式檔以及設計工具,詳細記錄了為了達成目標所採用的方法,以確保終端客戶可快速地在最低風險之下達到相同的實作結果。