在半導體產業裡,每數年就會出現一次小型技術革命,每10~20年就會出現大結構轉變的技術革命。而今天,為半導體產業所帶來的革命,並非是將製程技術推向更細微化與再縮小裸晶尺寸的技術,而是在封裝技術的變革。從2016年開始,全球的半導體技術論壇、各研討會幾乎都脫離不了討論FOWLP (Fan Out Wafer Level Package)這項議題。FOWLP會為整個半導體產業帶來如此大的衝擊性,莫過於一次就扭轉了未來在封裝產業上的結構,在在影響了整個封裝產業的製程、設備與相關的材料,也將過去前後段鮮明區別的製程,將會融合再一起,極有可能如同過去的液晶面板廠與彩色濾光片廠的歷史變化,再一次出現重演。

FOWLP (Fan Out Wafer Level Package)顧名思義就是和現有WLP的Fan In有著差異性,最大的特點是在相同的晶片尺寸下,可以做到範圍更廣的重分佈層(Redistribution Layer),基於這樣的變化,晶片的腳數也就將會變得更多,使得未來在採用這樣技術下所生產的晶片,其功能性將會更加強大,並且將更多的功能整合到單晶片之中,同時也達到了無載板封裝、薄型化以及低成本化等等的優點。

使得三星電子敗退於A10處理器的FOWLP封裝技術

在討論FOWLP(Fan-Out Wafer Level Packaging)封裝技術之前,先簡單的說明FOWLP封裝技術,若對這些先進技術尚不熟悉的話,也可藉此了解一些關於FOWLP的概廓。

基本上,FOWLP封裝技術原本是由德國Infineon Technologies所自行開發出來的封裝技術,當初寄望成為新世代封裝技術之一而受注目,但是由於種種的關係,使得整體良率過低,因此無法達到普及的程度,但FOWLP並非就此消失,而是深刻的留在各大半導體企業的心中,同時也默默地進行各項改進以及調整。

例如,台積電採用此一技術做為基礎,並且加以改進。使得台積電在2016年,全面利用自行所開發的扇出型晶圓級封裝(InFO FOWLP ; Integrated Fan Out FOWLP」為APPLE生產封裝新一代iPhone 7/7Plus所需的A10處理器。此舉備受全球業界的注目,同時刺激了全球各大半導體企業加速了FOWLP封裝技術的開發。

| 圖一 : 採用FOWLP晶圓級封裝所生產的A10處理器為台積電搶下APPLE訂單 |

|

在此之前,Apple針對iPhone所需的處理器是分別透過台積電和三星電子代工生產,然而由於三星電子在FOWLP技術上的開發進度遲緩,並且落後於台積電,因而台積電拿下了Apple在iPhone 7/7Plus所需A10處理器的所有訂單。

而三星電子方面,原本對於FOWLP封裝技術的態度是相當的消極,這是因為對於目前本身所擁有的層疊封裝技術(PoP ; Package on Package)是相當有自信心,自信有能力持續站在領先的地位。但是當因為台積電出現扇出型晶圓級封裝技術,而導致痛失APPLE的A10處理器之後,三星電子對於封裝技術方面,也出現了研發態度的轉變。

首先,三星電子攜手其集團旗下的三星電機(SEMCO),以成功開發出面板等級(Panel Level)的FO封裝技術-FOPLP(Fan-Out Panel Level Packaging)為首要目標,三星電機(SEMCO)是三星集團下以研發生產機板為主的企業,集團內所有對於載板在技術或材料上的需求,均由三星電機主導開發。雖說如此,儘管三星電子全力研發比FOWLP更進步的「扇出型面板級封裝」(Fan-out Panel Level Package、FoPLP),但估計仍需一兩年時間才能採用。

| 圖二 : 三星電子全力發展FOPLP製程技術期望在APPLE的下一代處理器扳回一城 |

|

半導體業界關注的FOWLP封裝技術究竟為何

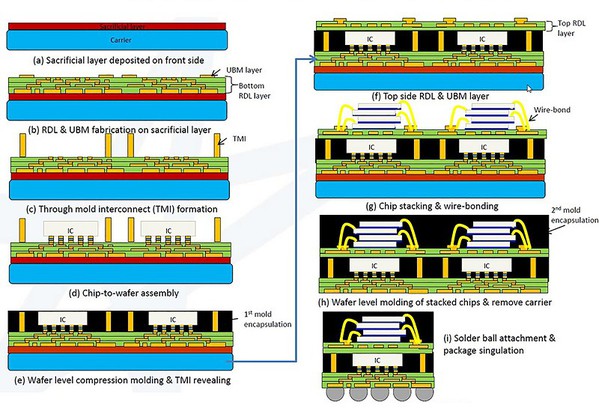

基本上,參考FOWLP封裝技術的簡略示意圖。在晶圓的製程中,從半導體裸晶的端點上,拉出所需的電路到重分佈層(Redistribution Layer),進而形成封裝。在這樣的基礎上就不需要封裝載板,更不用打線(Wire)以及凸塊(Bump),進而得以降低30%的生產成本,以及減少晶片的厚度。

| 圖三 : 從半導體裸晶的端點上,拉出所需的電路到重分佈層進而形成封裝,就是所謂的FOWLP封裝技術 |

|

在晶片中的重分佈層會因為縮短電路的長度,使得電氣訊號大幅度的提高。在過去,對於WLCSP的半導體晶片面積和封裝面積是相同的來比較,FOWLP技術下的晶片的面積比原本封裝後面積小很多,因此,可以完成更多腳位設計,或是大大減少封裝後半導體晶片的面積,達到小型化晶片的需求。使得原本需要數顆生產成本較高的直通矽晶穿孔(TSV ; Through-Silicon Via),進化到能將不同的元件透過封裝技術整合在一起,並且小型化的SiP(System in Package)封裝技術。

為了形成重分佈層,必須將封裝製程導入晶圓的前段製程,因此也打破了固有前段製程與後段製程藩籬,這對於晶片生產者來說如何完成到一貫性的製程技術(Full Turnkey)就顯得相當重要。在此之下,封裝代工業者以及封裝載板材料業者或許就會出現是否能繼續存活下去的關鍵問題。因此,對於未來的半導體世界來說,決勝手段已不是僅僅只是在5奈米、3奈米製程細微化的能力,而是已經延伸到前後段製程的一貫性的製程技術。

而在半導體先進製程技術上落後台積電的三星電子,如果無法追上台積電的話,那麼在iPhone的這個訂單競賽中將不會存在任何的機會性。同時在這個商業競賽中,不僅僅只有晶片代工廠的競爭,同時也是半導體製程設備以及材料業者間的競爭。

FOWLP到底有多大的市場規模

飽受眾人所注目的FOWLP封裝技術,雖然得以大幅度簡化過去需要複雜製程的封裝工程,但是,在矽晶圓部分(前段製程),還是必須利用濺鍍以及曝光來完成重分佈層。到今天為止,在先進的封裝製程技術上無論是從覆晶封裝(Flip Chip),還是2.5D/3D領域的直通矽晶穿孔技術,製作困難度都不斷的增加,投入成本也一直在增加,因此如果想直接跨入FOWLP封裝技術領域,實在很難期望一步就能夠達成。

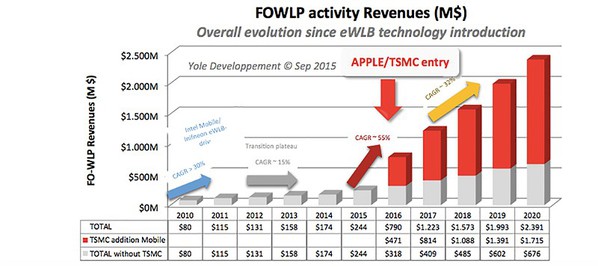

不過雖然如此困難,但各大半導體業者仍舊持續投入大量的研發成本,為的就是期望能早一日進入這一個先進的封裝世界。尤其在台積電在利用FOWLP這個封裝技術拿下了APPLE所有iPhone 7的A10處理器而受到注目之後,相信未來並不是只有APPLE,而是所有新一代的處理器都將會導入FOWLP這一個封裝製程。

根據市場調查公司的研究,到了2020年將會有超過5億顆的新一代處理器採用FOWLP封裝製程技術,並且在未來,每一部智慧型手機內將會使用超過10顆以上採用FOWLP封裝製程技術生產的晶片。市場調查公司相信,在未來數年之內,利用FOWLP封裝製程技術生產的晶片,每年將會以32%的年成長率持續擴大其市場佔有,到達2023年時,FOWLP封裝製程技術市場規模相信會超過55億美元的市場規模,並且將會為相關的半導體設備以及材料領域帶來22億美元以上的市場潛力(圖四)。

| 圖四 : 到達2023年時,FOWLP封裝製程技術市場規模將會超過55億美元 |

|

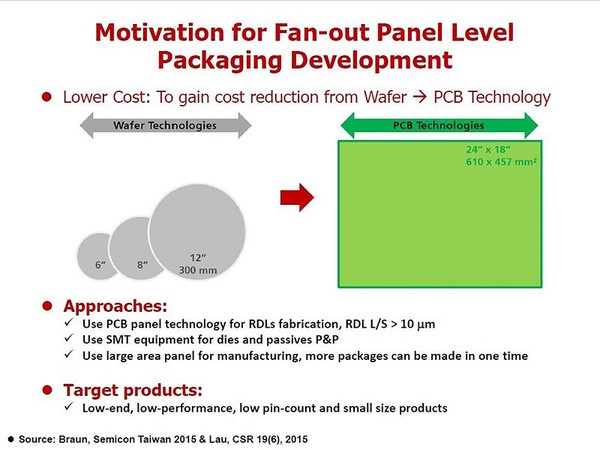

FOPLP可以量產出數倍於300毫米矽晶圓晶片產品

FOPLP封裝技術是基於具有整合前後段半導體製程,FOWLP技術的延伸突破性技術,晶圓製程上採用FOWLP技術的話,在直徑為300毫米(mm)晶圓上的矽裸晶(Silicone Die),可以將前後段製程整合進行,並且可以將其視為一次的封裝製程,大幅度的降低製程生產與材料等等的各項成本。

但是如果能夠在比300毫米晶圓更大面積的面板(方形面積的載板)上進行FO製程的話,那麼就被稱為FOPLP封裝技術,這樣的技術無論是印刷載板,或者例如是液晶面板用的玻璃載板上,都可以適用。

以目前而言,比300毫米(mm)矽晶圓更大的載板,包括了例如像610mm×457mm印刷載板,和這樣的面積相比較,300毫米(mm)矽晶圓的面積約為707mm2,而610mm×457mm卻可以達到約2788mm2,這大約是300毫米(mm)矽晶圓的4倍面積,而可以簡單的視為在一次的製程下,就可以量產出4倍於300毫米(mm)矽晶圓的晶片產品(圖五)。

| 圖五 : FOPLP在一次610mm×457mm印刷載板的製程下,就可以量產出4倍於300毫米(mm)矽晶圓的晶片產品 |

|

當然如果期望達到在如此高密度下量產時,並且將後段封裝製程整合進去時,那麼重分佈層(Redistribution Layer)的製程技術就變得不可或缺。例如,在印刷載板上使用FOPLP技術,不僅僅考驗著印刷載板的製程能力,特別在高密度的佈線結構時,所需要的增層(Buildup)佈線工程,就必須仰賴重分佈層(Redistribution Layer)的完成。以目前來說,線距大多是在10微米(μm)以上,但是一但進入到了晶圓等級FOWLP技術的製程時,重分佈層的密度就會比一般更高,這時線距大多便成了是5微米(μm)以下。

材料供應商需調整其研發方向,才可持續地扮演關鍵性的地位

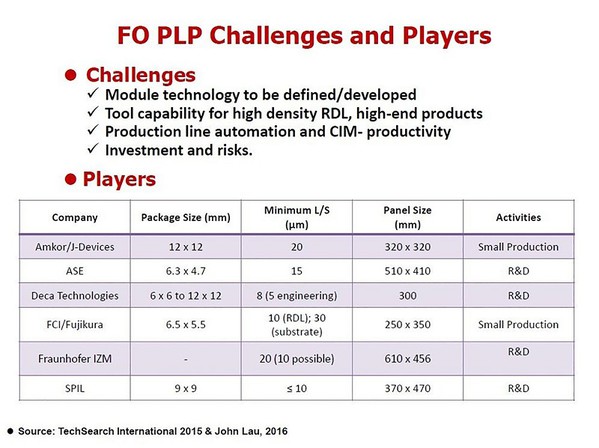

目前積極投入FOPLP製程技術的半導體企業包括了,三星電子、J-DEVICES、FUJIKURA、日月光(ASE ;Advanced Semiconductor Engineering)、DECA TECHNOLOGIES、 SPIL(Siliconware Precision Industries)..等等(圖六)。

| 圖六 : 全球各大封裝業者均積極投入FOPLP製程技術 |

|

業界也有人猜想,三星電子相當有可能重新修改較舊的LCD濺鍍、曝光等等的設備,來進行FOLPL的封裝製程,由於能夠達到更大面積的生產,一般認為這樣的面積下量產出來的晶片成本,或許將會比台積電更低更具競爭力。藉由和集團的三星電機合作,共同面對台積電的競爭,來爭奪APPLE的下一代處理器機會。

面對半導體製程技術不斷的革新與整合,使得使用載板的封裝比例逐漸呈現減少的趨勢,根據市場研究機構的統計,載板的封裝比例已經由2010年的51%降低到2015年的39%。而不需使用載板的晶圓級的封裝比例,則是由2010年的2%大幅度的攀升至2015年的26.7%。

因此,伴隨著半導體量產與封裝技術的演進,原本是扮演著不可或缺角色的封裝材料供應商(包括載板),也逐漸在技術演進的下,市場將急速的萎縮。此時,封裝材料供應商需調整其研發方向,並逐漸向前段製程跨進以及布局,才可在技術急遽演進的潮流中,持續地扮演關鍵性的地位。