當延續摩爾定律的開發重點,也就是單一晶片電晶體數量的世代更迭仍因技術受阻而放緩,未來晶片市場逐漸開始擁抱小晶片的設計思維,透過廣納目前供應鏈成熟且靈活的先進製程技術,刺激多方廠商展開更多合作,進一步加速從設計、製造、測試到上市的流程,讓更多高效節能的晶片與物聯網成真。

要說目前市場上最主流的晶片設計,必非「系統單晶片(SoC)」莫屬。就這點,近年最廣為熱論的焦點就鎖定蘋果2020年推出基於Arm架構的自製晶片M1,而日前盛大舉行的蘋果2021年首場全球新品發布會中,最新一代iMac更揭曉為繼MacBook之後採用M1的第二波產品之一,SoC更被點名,它就是iMac超輕薄吸睛外型的設計關鍵。

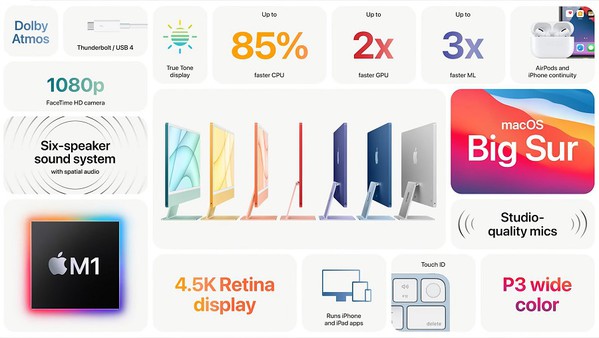

蘋果M1把CPU、GPU、記憶體、I/O等元件全部整合在同個晶片上,目標是針對晶片性能、功耗和尺寸(PPA)全面進一步提升,結果確實也達到了整體系統效能優化的突破性成果。iMac除了尺寸更輕薄,在效能方面,CPU最高增加了85%,GPU最多提升至兩倍,就連備受矚目的AI機器學習,甚至能升級至三倍。

| 圖一 : 蘋果首款自製晶片M1就採用SoC設計,由於CPU、GPU等元件在製造與運作上都更緊密互連,產品的效能、功耗和尺寸全部都能支援顯著的升級。圖為最新iMac的產品特色與性能升級。(source:Apple) |

|

採用SoC設計的優勢就是這麼誘人,可以一次滿足常被談到的晶片性能三大指標,在在彰顯其在晶片設計坐穩主流地位的關鍵。

但問題是,半導體發展至今,不僅負責不同功能的各類元件種類更多,包含如5G等無線通訊、AI加速,以及智慧應用所需的語音、影像、溫度感測等功能,這些在以往並非設計所需。

這些元件帶給先進製程的生產挑戰也更為嚴峻。電晶體是更小了,但整體系統卻因需要整合更多元件而變得更大,良率會因此下降—想像一下,越大的靶,中槍陣亡的機率更高;開發成本也正變得越來越昂貴,不論是時間或資金,都導致意欲跟進新興市場的IC業者難以跨越這道競爭門檻。

因此,考量未來產品應用的需求轉變,以及目前製程技術的顯見瓶頸,摩爾定律關注的電晶體密度與閘極微縮,很可能不再是未來晶片開發的首要重點,更有可能的是,晶片設計的靈活性、整合性和即時性將成為一股新風潮,從SoC這種單片(monolithic)的設計思維,趨動邁向模組化(modular)與異質性(heterogenous)的方向發展,這不僅能最大程度活化現有的供應鏈資源,更重要的是,可以更順利地因應物聯網對晶片的爆炸性需求。

從CPU到GPU,小晶片可行性持續拓展

小晶片趨勢的進展速度非常驚人。市調機構Omdia就相當看好小晶片市場,2020年時他們預估,小晶片在半導體製造領域將在未來四年以九倍的速度成長,2024年產值達到58億。未來,半導體產業也能藉此回復到晶片每兩年推新進展的經濟循環。

小晶片架構的應用範圍極廣,包含MPU、GPU、PLD以及SoC都能導入這項新的設計思維。目前全球有越來越多半導體廠商與國家級研究單位開始採取這條另闢蹊徑的晶片開發策略,甚至包含曾經對多晶片模組(multi-chip module;MCM)十分不以為然的Intel,它現在可是搖身變成小晶片市場的主要開發者之一,而且持續積極號召產業夥伴投入開發更多基於小晶片的產品。

先進封裝是小晶片的推手 也是先決條件

Intel曾經坦言,早在開發雙核處理器Pentium D和四核處理器Core 2時,他們就採取了將兩顆小晶片放在同一晶片上的做法,前者用的是Pentium 4,後者是Core 2 Duo。因為M2M架構可以減少設計複雜度、相關問題以及把問題複雜化的情況,而這些卻是用單片核心(monolithic core)設計必須面對的固有問題。

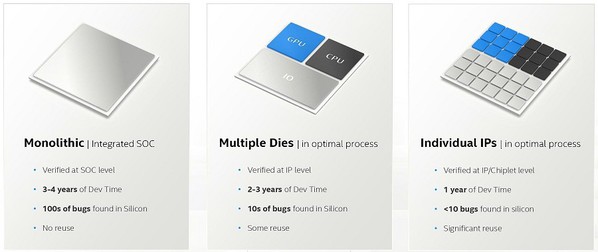

| 圖二 : 針對晶片設計的未來發展,Intel預期將從系統單晶片邁向小晶片架構,驗證會逐步從IP等級細緻化至小晶片等級,開發時間能從現在的3~4年大幅縮短成1年內,單顆晶片的瑕疵也能從上百個改良至個位數。(source:Intel) |

|

小晶片架構把目前的主流設計思維分區解構,問題因此由繁化簡,不過若想達到系統效能、成本與尺寸的極致優化,卻也不是把大晶片切割再拼貼就能滿足,小晶片的未來發展,主要就看半導體廠商的封裝技術與介面連接技術。

Omdia分析師Tom Hackenberg就指出,小晶片採取的策略是用更多晶片來增加電晶體數量,剛好避開了摩爾定律在單一晶片上放更多電晶體的發展途徑,利用封裝,就能把多個小晶片整合起來。

顯見封裝技術無疑是開發小晶片時首先浮現的先決考量。在這個領域,Intel與台積電是長久以來的兩大名將,雙方對市場與專業技術常有所見略同的洞察,因此解決方案也不可免地互別苗頭。在2.5D封裝,分別提出了利用橋接互連的EMIB以及導入中介層的CoWoS技術,在3D封裝則有Foveros和InFO技術。

標準化介面是產業共同的下一步

有了這些先進封裝技術,小晶片的應用要拓展與創新增添了許多可能,同時,現階段產業也在努力達成小晶片開發的另一個目標,就是晶粒之間(D2D)的介面連接技術,目標是增加小晶片之間的傳輸頻寬,同時確保這些偕同運作的功耗更省電,也就是精進小晶片設計的效能與功耗表現。

市場上現有的幾個D2D介面解決方案都聚焦在實體層(PHY)。Intel就與美國國防部DARPA緊密合作,發展開源的AIB(Advanced Interface Bus)匯流排架構,近期也公開了AIB 2.0的初步規格,不僅要增加每通道的IO數量,微凸塊(microbump)的尺寸也要更小,其矩陣面積可以比上一代標準還小一半,整體頻寬密度就能提升六倍。

AIB匯流排架構的開源性質也顯示了硬體界的新氣象,AIB 2.0的規格就是由Google號召成立的CHIPS聯盟(CHIPS Alliance)宣布推出,成員還包括三星、阿里巴巴、威騰(Western Digital)、明導國際(Mentor)和SiFive等。

CHIPS聯盟藉由提供矽基元件和FPGA的開源硬體設計,希望能夠創造開放合作的開發環境來降低研發成本,而小晶片概念的初衷,也呼應了半導體供應鏈在共同面對開發成本與技術挑戰時的迫切需求。「業界對小晶片的開發需求來自幾個面向,包含標準化的介面,更確切的說,是一個標準化的實體層,而且必須利用特定的製程或封裝技術來展示應用範例,要做到這些,我們也需要EDA生態系的支援。」CHIPS聯盟執行長Rob Mains表示。

SiFive旗下負責ASIC與IP開發的事業單位OpenFive也推出HBM/D2D解決方案,近期更宣布,利用其HBM3與D2D介面IP、SiFive的32位元Risc-V核心以及台積電5nm製程,已成功完成晶片設計(tape-out),能夠打造高效能的小晶片,將多個晶片整合,或利用中介層完成2.5D封裝,應用鎖定高效能運算、AI運算、網路或儲存等熱門應用。

可以想見,小晶片從FPGA、CPU將一路擴展至GPU、APU等元件開發上,近年屢次以創新技術大舉推出物美價廉處理器競品的AMD也是小晶片的主要開發商,其採用Zen 2架構的EPYC處理器就成功地把負責主要運算和處理其他連接或控制功能的元件區隔開來,整合7nm與14nm各自的效能與成本優勢。下一步他們更將進擊GPU領域,除了要讓小晶片之間的連接設計能確保記憶體的資料同步,與CPU連接的匯流排技術也會是未來關注的重點。

台灣AI供應鏈 也能是小晶片供應鏈

那麼,台灣供應鏈在小晶片發展上的舞台會在哪?目前採用小晶片設計的產品多半還是鎖定主要的邏輯和記憶體功能,其他功能區塊或AI加速器會是接下來努力實現的方向,但要做到這點其實頗有難度,除非與第三方,也就是其他半導體公司合作。

工研院資訊與通訊研究所所長闕志克日前在2021 VLSI研討會上就點出,全球在AI與5G物聯網的浪潮下,對AIoT的需求將會大幅攀升,面對新一代晶片少量多樣的特性,傳統晶片設計模式將轉變為「小晶片系統設計」。

| 圖三 : 工研院主辦的VLSI國際研討會日前盛大展開,剖析AI、新興記憶體與小晶片系統的最新發展(source:itri.org.tw)。 |

|

AI晶片市場,是台灣半導體供應鏈未來共同的戰略要塞,再結合小晶片趨勢,或許就能匯聚出邏輯、記憶體與感測領域的加乘效益。目前工研院發展了AI晶片的軟硬體設計平台,並與國內的IC設計及晶圓廠合作,開發以小晶片為基礎的新一代AI晶片,包含具備記憶體開發技術的力積電,以及佈局感測晶片與IP技術市場的凌陽,目前皆已與工研院展開合作。

闕志克表示:「台灣半導體在全球供應鏈中具備相當完整的開發資源,利用像是台積電10nm以下的先進製程,可以實現高效能運算應用,但相對地,這些先進晶片的製造與IP授權成本也較高,隨著摩爾定律走到3nm以下,小晶片系統與先進封裝會是關鍵的下一步,為後摩爾時代開創半導體產業的全新機會。」

他指出,工研院已經起先部署台灣的「小晶片生態系統」,未來IC業者可以透過封裝技術,將多個晶片IP整合在同一封裝,晶片設計也能由20%自行開發、80%由外部第三方的方式供應,半導體製造商的商業模式也將更多元,IP授權可以不再是鉅額投資,而是依照銷售量定價。

「用多少算多少,就能減輕IC設計業者在開發初期的負擔,這對tier 2或tier 3的業者來說是很好的契機。」闕志克表示。

結語

小晶片是未來晶片設計的明日之星,隨著先進封裝與介面連接技術創新雙管齊下,未來可望看見運算單元與記憶體單元分別由不同業者設計,各自還能以最適合的製程生產,再以先進封裝技術加以整合,最終實現邏輯與記憶體之間更高效能的資料傳輸,還能用更低成本、更高彈性的方式加速AI晶片上市。台灣的半導體供應鏈具備地域與先進技術的多重優勢,掌握這波小晶片趨勢,更能以多元化的商業模式在國際市場拓展商機。

**刊頭圖(source:amd.com)