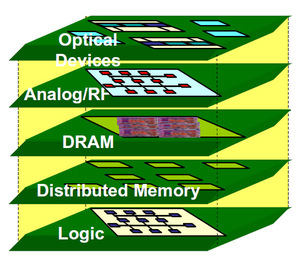

在芯片微型化的过程中,兼具效能是非常关键的目标。如何在更小的芯片尺寸中,塞进更多的功能,一直是半导体业者所努力的研发方向。而所谓的「3D IC」制程,也是在此前提下所产生的技术,除了逻辑电路的微型化之外,还企图将内存、MEMS与射频芯片等芯片也一并以3D堆栈的方式,整合至单一个芯片中,此法不但能缩小体积,在应用与性能上也超过传统的芯片,也因此3D IC被认为是次世代的主流芯片技术之一。  | | 所谓的「3D IC」制程,也是在此前提下所产生的技术,除了逻辑电路的微型化之外,还企图将内存、MEMS与射频芯片等芯片也一并以3D堆栈的方式,整合至单一个芯片中 |

然而,3D IC技术提出至今,除了在CMOS影像传感器和内存领域有初步的成果之外,在其它的市场上依然没有任何商用的契机出现,而要推演至真正使用3D IC的系统产品上市,那更是遥遥无期。其中的关键点,除了生产设备商与芯片业者必须积极推动之外,EDA工具与量测厂的加入也关键至极。因此,相关上中下游的业者如何齐聚起来,并在短时间内催生一套实用的标准,将决定3D IC日后发展的盛与衰。 那3D IC究竟为什么如此难以突破呢?目前的困难点不外乎几个。首先,芯片3D堆栈的散热问题仍难以克服。由于传统的平面芯片可以着靠散热片或者铜线来进行散热,但当芯片必须堆栈的时候,散热问题则会因堆栈的芯片彼此传热而加重,并造成封装与系统设计上的困难。现在业界仍没有一个适合商用的对策,因此也减缓了3D IC的发展。 再者,EDA工具商介入太少也是主因之一。现在台面上有能力生产3D IC的厂商,几乎都是in house的方式,属于闭关练功的状态。这些公司所使用的设计工具都是自行开发或者土法炼钢,并没有一套专为3D IC开发所设计的工具可用。多家从事3D IC的业者就指出,缺乏EDA工具是目前3D IC普及的一大障碍,若有一套专用的自动化工具,不但能大幅减少开发时间,也能建立起业者彼此沟通的平台。 其三,则是量测与验证工具的缺乏。也同样在业者各唱各调的状况下,目前并没有一套量测标准和测试验证设备可为3D IC做背书,仅靠各家提出的产品数据,将难以取信客户与市场;而没有专属的量测工具,对于生产流程和质量良率的建立也将是困难重重。以上这几个问题都是3D IC想更进一步发展,所必须立即突破的障碍。 对于3D IC的制程也兴趣浓厚的晶圆代工厂台积电就曾表示,3D IC在未来10年内将很难出现大规模普及。因要在单一个芯片内盖出平房、楼房和地下室这绝非易事,而且这也不是单一业者可以做到,必须整个产业一起进行才有可能。加上还必须考虑到成本与市场的因素,因此短期间内难有作为。但台积电也指出,建立标准绝对是第一步。 |